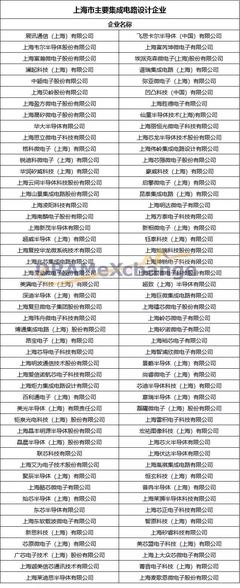

專用集成電路(ASIC)設計是當代電子工程與半導體產業的核心領域之一,它專注于為特定應用定制高性能、低功耗的集成電路解決方案。本教程旨在提供一份實用的入門指南,幫助讀者理解ASIC設計的基本流程、關鍵技術和實際應用。

一、ASIC設計概述

專用集成電路(ASIC)與通用集成電路(如微處理器)不同,它是為特定功能或系統量身定制的芯片,廣泛應用于通信、消費電子、汽車電子、醫療設備等領域。ASIC設計涉及從概念到物理實現的完整過程,包括需求分析、架構設計、邏輯實現、物理布局、驗證和測試等環節。其優勢在于優化性能、降低功耗和成本,但開發周期較長且初始投資較高。

二、設計流程與階段

ASIC設計通常遵循標準化的流程,主要分為以下幾個階段:

- 需求分析與規范定義:明確芯片的功能、性能指標(如速度、功耗、面積)和接口要求,編寫詳細的設計規范文檔。

- 架構設計:根據規范,確定芯片的整體結構,包括模塊劃分、數據流控制、時鐘和電源管理策略等。

- 邏輯設計:使用硬件描述語言(如Verilog或VHDL)進行寄存器傳輸級(RTL)編碼,實現功能邏輯。此階段注重代碼的可綜合性和可驗證性。

- 功能驗證:通過仿真和形式驗證方法,確保RTL設計符合規范。常用工具包括仿真器(如ModelSim)和驗證語言(如SystemVerilog)。

- 綜合與優化:將RTL代碼轉換為門級網表,并利用約束(如時序、面積)進行邏輯優化,生成初步的物理設計基礎。

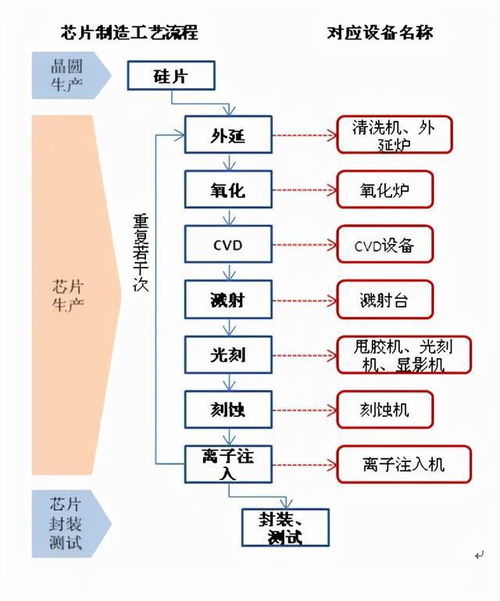

- 物理設計:包括布局規劃、時鐘樹綜合、布線、寄生參數提取和時序分析等步驟,確保芯片滿足制造要求。工具如Cadence Innovus或Synopsys IC Compiler被廣泛使用。

- 驗證與簽核:進行物理驗證(如DRC、LVS)和時序簽核,確保設計無誤后,生成GDSII文件交付給晶圓廠。

- 測試與量產:設計測試向量,進行芯片測試和故障分析,最終實現批量生產。

三、關鍵技術要點

- 低功耗設計:隨著移動設備和物聯網的普及,功耗成為關鍵指標。技術包括電源門控、多電壓域、動態電壓頻率調整(DVFS)等。

- 時序收斂:在高性能設計中,時鐘偏移和路徑延遲必須嚴格控制,通過優化時鐘樹和約束管理來實現。

- 可制造性設計(DFM):考慮工藝變異和缺陷,提高芯片良率,涉及規則調整和冗余設計。

- 驗證方法學:采用基于UVM(通用驗證方法學)的驗證環境,提升驗證效率和覆蓋率。

四、實用工具與資源

ASIC設計依賴專業軟件工具鏈,主流供應商包括Cadence、Synopsys和Mentor Graphics(現為Siemens EDA)。初學者可以從開源工具(如Yosys用于綜合)和在線課程入手,同時參考行業標準文檔(如IEEE標準)和實際案例。

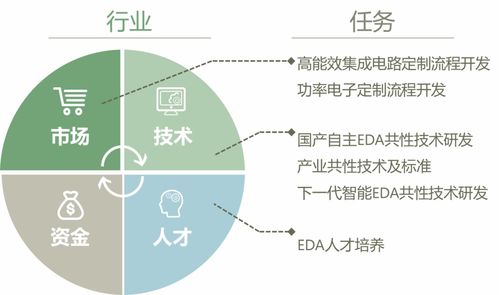

五、發展趨勢與挑戰

未來ASIC設計將面臨工藝節點不斷縮小(如3nm以下)、異構集成(如Chiplet技術)和人工智能驅動的自動化設計等趨勢。挑戰包括設計復雜性增加、成本上升和人才短缺,因此持續學習和實踐至關重要。

###

專用集成電路設計是一個多學科交叉的領域,要求工程師具備扎實的電子學基礎、編程技能和系統思維。通過本教程,希望讀者能建立起ASIC設計的整體框架,并進一步探索實際項目,從而在快速發展的半導體行業中立足。建議結合具體設計工具和實驗,加深對理論知識的理解,最終實現從理論到實踐的跨越。