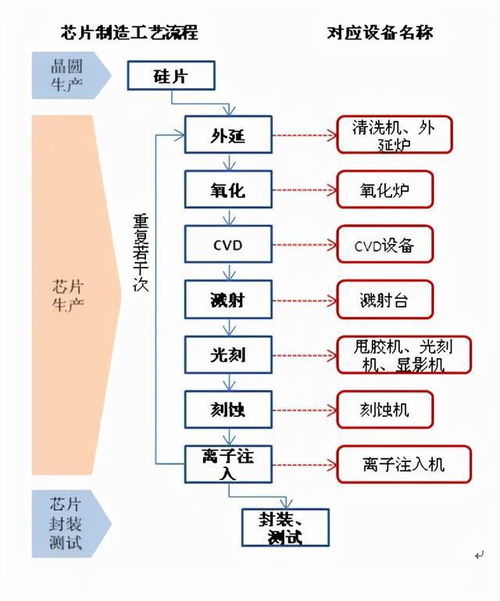

集成電路設(shè)計(jì)是一個(gè)將抽象概念轉(zhuǎn)化為物理實(shí)體的復(fù)雜過程,通常可分為前端設(shè)計(jì)和后端設(shè)計(jì)兩大階段。前端設(shè)計(jì)側(cè)重于邏輯功能與架構(gòu),而后端設(shè)計(jì)——即物理設(shè)計(jì)——?jiǎng)t是將經(jīng)過驗(yàn)證的邏輯網(wǎng)表轉(zhuǎn)化為可用于芯片制造的、具有精確幾何形狀和物理連接的版圖。物理設(shè)計(jì)是連接電路設(shè)計(jì)與芯片制造的橋梁,其質(zhì)量直接決定了芯片的性能、功耗、面積和可靠性。

物理設(shè)計(jì)的主要目標(biāo)是在滿足一系列嚴(yán)苛約束(如時(shí)序、功耗、面積、信號完整性等)的前提下,實(shí)現(xiàn)邏輯電路在硅片上的最優(yōu)布局與布線。這個(gè)過程通常包含以下幾個(gè)核心步驟:

- 布圖規(guī)劃:這是物理設(shè)計(jì)的起點(diǎn),如同建筑設(shè)計(jì)的總體規(guī)劃。設(shè)計(jì)者需要確定芯片的核心區(qū)域、輸入輸出(I/O)引腳位置、宏模塊(如存儲器、處理器核)的擺放,以及電源網(wǎng)絡(luò)的初步規(guī)劃。一個(gè)好的布圖規(guī)劃能為后續(xù)步驟奠定堅(jiān)實(shí)基礎(chǔ),有效優(yōu)化芯片面積和布線擁塞。

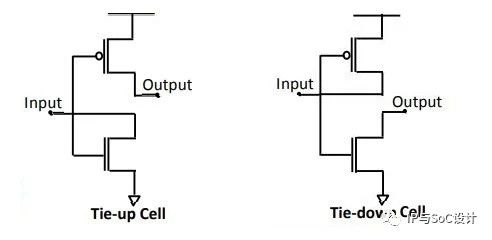

- 布局:在此階段,標(biāo)準(zhǔn)單元(實(shí)現(xiàn)基本邏輯功能的預(yù)設(shè)計(jì)單元)被準(zhǔn)確地放置到芯片的規(guī)劃區(qū)域內(nèi)。布局的目標(biāo)是減少關(guān)鍵路徑的延遲、降低布線擁塞,并優(yōu)化功耗。布局算法需要綜合考慮單元間的連接關(guān)系、時(shí)序要求以及散熱等因素。

- 時(shí)鐘樹綜合:時(shí)鐘信號是芯片的“心跳”,需要同步到達(dá)所有時(shí)序單元。時(shí)鐘樹綜合的目的是構(gòu)建一個(gè)低偏差、低延遲的時(shí)鐘分布網(wǎng)絡(luò),確保時(shí)鐘信號能快速、一致地送達(dá)芯片各處,這是保證芯片在高頻下穩(wěn)定工作的關(guān)鍵。

- 布線:這是將布局好的單元按照邏輯連接關(guān)系用金屬線實(shí)際連接起來的過程。布線通常分為全局布線和詳細(xì)布線兩步。全局布線規(guī)劃連接的大致路徑和通道分配,而詳細(xì)布線則生成符合設(shè)計(jì)規(guī)則的精確幾何圖形。布線必須規(guī)避信號串?dāng)_、電遷移等問題,并滿足嚴(yán)格的時(shí)序要求。

- 物理驗(yàn)證與簽核:在版圖生成后,必須進(jìn)行一系列嚴(yán)格的驗(yàn)證,以確保其可制造且功能正確。這包括:

- 設(shè)計(jì)規(guī)則檢查:確保版圖符合芯片制造工藝的物理限制(如線寬、間距)。

- 電氣規(guī)則檢查:檢查是否存在短路、開路等電氣錯(cuò)誤。

- 版圖與電路圖一致性檢查:確保物理版圖與原始邏輯電路圖在功能上完全一致。

- 時(shí)序、功耗與信號完整性簽核:使用提取出的實(shí)際寄生參數(shù)進(jìn)行最終仿真,確認(rèn)芯片在時(shí)序、功耗和信號質(zhì)量方面滿足所有規(guī)格要求。

面臨的挑戰(zhàn)與趨勢

隨著工藝節(jié)點(diǎn)不斷微縮至納米甚至更小尺度,物理設(shè)計(jì)面臨著前所未有的挑戰(zhàn):

- 物理效應(yīng)加劇:寄生電阻電容、信號串?dāng)_、電源噪聲、工藝偏差等效應(yīng)的影響變得極為顯著,必須在設(shè)計(jì)階段精確建模和優(yōu)化。

- 設(shè)計(jì)復(fù)雜度劇增:數(shù)十億晶體管的集成度使得設(shè)計(jì)空間探索和優(yōu)化難度呈指數(shù)級增長。

- 功耗與散熱:功耗密度攀升,低功耗設(shè)計(jì)和熱管理成為核心考量。

為應(yīng)對這些挑戰(zhàn),物理設(shè)計(jì)領(lǐng)域正積極擁抱新技術(shù):

- 人工智能與機(jī)器學(xué)習(xí):AI被用于預(yù)測擁塞、優(yōu)化布局布線、加速設(shè)計(jì)空間探索,大幅提升設(shè)計(jì)效率與質(zhì)量。

- 高層次綜合與物理感知設(shè)計(jì):前端設(shè)計(jì)與物理設(shè)計(jì)的界限變得模糊,在設(shè)計(jì)早期就考慮物理實(shí)現(xiàn)的影響,實(shí)現(xiàn)更好的協(xié)同優(yōu)化。

- 先進(jìn)封裝與芯粒技術(shù):通過2.5D/3D集成和芯粒(Chiplet)設(shè)計(jì),從系統(tǒng)層面突破單芯片的限制,這也對物理設(shè)計(jì)提出了新的跨芯片協(xié)同優(yōu)化要求。

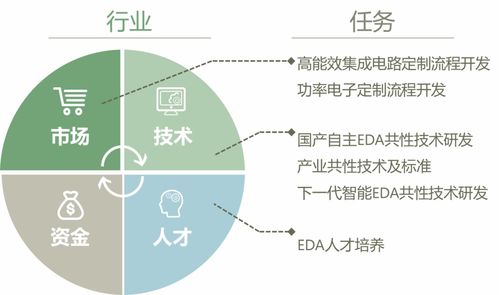

物理設(shè)計(jì)是集成電路設(shè)計(jì)中技術(shù)密集、承上啟下的關(guān)鍵環(huán)節(jié)。它不僅是將電路“畫”出來的藝術(shù),更是一門在納米尺度上平衡性能、功耗、面積和成本的精密科學(xué)。隨著技術(shù)的發(fā)展,物理設(shè)計(jì)工程師需要與工藝、架構(gòu)、EDA工具開發(fā)者更緊密地協(xié)作,共同推動(dòng)芯片產(chǎn)業(yè)向更高性能、更低功耗和更強(qiáng)功能的方向邁進(jìn)。