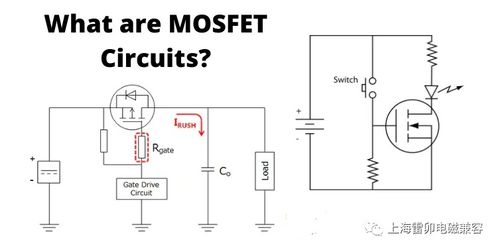

在當(dāng)代集成電路設(shè)計(jì)的宏大版圖中,金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管(MOSFET)無(wú)疑是構(gòu)筑所有數(shù)字與模擬系統(tǒng)的基石。無(wú)論是智能手機(jī)中高速運(yùn)算的處理器,還是電動(dòng)汽車?yán)锔咝У哪芰抗芾硇酒鋬?nèi)部都密布著數(shù)以億計(jì)的MOSFET。理解MOSFET的工作原理、特性及其在電路設(shè)計(jì)中的應(yīng)用,是每一位集成電路工程師的必修課。

一、MOSFET:從物理結(jié)構(gòu)到電氣特性

MOSFET是一種通過電場(chǎng)效應(yīng)控制電流通斷的三端器件(源極、漏極、柵極)。其核心在于柵極下的溝道形成與夾斷。根據(jù)溝道類型,主要分為N溝道(NMOS)和P溝道(PMOS)。當(dāng)柵極電壓超過閾值電壓時(shí),導(dǎo)電溝道形成,器件開啟。這種電壓控制電流的特性,使其成為理想的開關(guān)和放大元件。

關(guān)鍵的電氣特性包括:

- 轉(zhuǎn)移特性:描述了漏極電流與柵源電壓的關(guān)系,決定了開關(guān)的閾值和跨導(dǎo)。

- 輸出特性:展示了漏極電流與漏源電壓在不同柵壓下的關(guān)系,區(qū)分了線性區(qū)、飽和區(qū)和截止區(qū)。

- 寄生參數(shù):如柵源/柵漏電容、源漏電阻等,這些參數(shù)直接決定了電路的開關(guān)速度、功耗和頻率響應(yīng),是高頻與高速電路設(shè)計(jì)中的關(guān)鍵考量。

二、CMOS技術(shù):現(xiàn)代數(shù)字電路的支柱

互補(bǔ)金屬氧化物半導(dǎo)體(CMOS)技術(shù)將NMOS和PMOS晶體管成對(duì)使用,構(gòu)成了當(dāng)今幾乎所有數(shù)字集成電路的基礎(chǔ)。一個(gè)基本的CMOS反相器由一個(gè)上拉的PMOS和一個(gè)下拉的NMOS組成。其最大優(yōu)點(diǎn)在于靜態(tài)功耗極低:在穩(wěn)定邏輯狀態(tài)下,總有一條通路被完全切斷,只有極微小的漏電流。這種低功耗特性使得高密度、超大規(guī)模集成成為可能。從邏輯門(與非、或非門)到觸發(fā)器,再到復(fù)雜的處理器內(nèi)核,都是由這些基本的CMOS單元組合、級(jí)聯(lián)而成。

三、模擬電路設(shè)計(jì)中的MOSFET藝術(shù)

在模擬集成電路中,MOSFET的角色從單純的開關(guān)演變?yōu)榫艿男盘?hào)處理元件。

- 放大電路:共源極、共柵極、共漏極(源極跟隨器)是三種基本組態(tài),用于實(shí)現(xiàn)電壓放大、電流緩沖和阻抗變換。設(shè)計(jì)需精心偏置晶體管進(jìn)入飽和區(qū),并權(quán)衡增益、帶寬、線性度和噪聲性能。

- 電流鏡與偏置電路:利用兩個(gè)或多個(gè)具有相同柵源電壓的MOSFET,可以精確復(fù)制電流,為整個(gè)芯片提供穩(wěn)定可靠的偏置參考,是模擬IC的“心臟”。

- 開關(guān)與模擬開關(guān):利用其近乎理想的開關(guān)特性(高關(guān)斷電阻、低導(dǎo)通電阻),用于采樣保持電路、數(shù)據(jù)轉(zhuǎn)換器和可編程增益放大器等。

- 射頻與混合信號(hào)設(shè)計(jì):在GHz頻率下,MOSFET的寄生電容、電感效應(yīng)變得至關(guān)重要。設(shè)計(jì)需要深入考慮噪聲系數(shù)、線性度(IP3)、匹配網(wǎng)絡(luò)和襯底耦合等復(fù)雜問題。

四、先進(jìn)工藝下的挑戰(zhàn)與設(shè)計(jì)考量

隨著工藝節(jié)點(diǎn)進(jìn)入納米尺度(如7nm、5nm乃至更小),MOSFET的設(shè)計(jì)面臨著前所未有的挑戰(zhàn):

- 短溝道效應(yīng):溝道長(zhǎng)度縮短導(dǎo)致閾值電壓漂移、漏致勢(shì)壘降低等,使器件的控制變得困難。

- 功耗墻:動(dòng)態(tài)功耗與CV2f成正比,而靜態(tài)功耗因亞閾值漏電流加劇而顯著上升。低功耗設(shè)計(jì)(如多閾值電壓、電源門控、近閾值計(jì)算)成為核心。

- 工藝變異:納米尺度下,原子級(jí)別的工藝波動(dòng)會(huì)導(dǎo)致器件參數(shù)(如閾值電壓、溝道長(zhǎng)度)出現(xiàn)顯著隨機(jī)偏差,設(shè)計(jì)必須具有足夠的工藝容差和魯棒性。

- 新型結(jié)構(gòu):為了延續(xù)摩爾定律,鰭式場(chǎng)效應(yīng)晶體管(FinFET)乃至環(huán)柵晶體管(GAAFET)等三維結(jié)構(gòu)已取代傳統(tǒng)平面MOSFET,以更好地控制溝道電流,減少漏電。

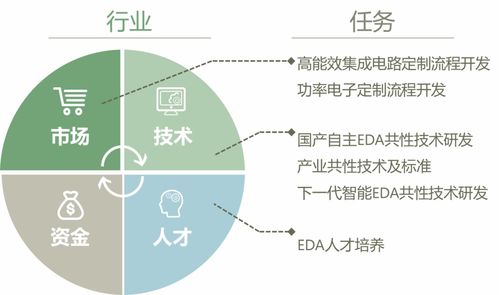

五、設(shè)計(jì)方法學(xué):從器件到系統(tǒng)

現(xiàn)代IC設(shè)計(jì)是一個(gè)高度分層和自動(dòng)化的過程:

- 電路級(jí)設(shè)計(jì):基于SPICE仿真,對(duì)MOSFET電路進(jìn)行直流、交流、瞬態(tài)和噪聲分析,優(yōu)化性能指標(biāo)。

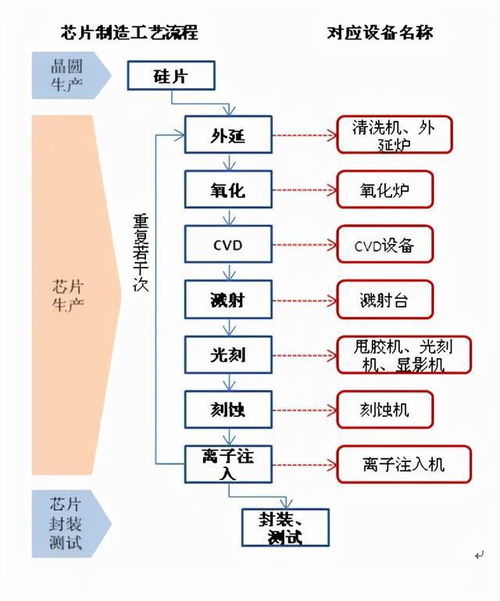

- 版圖設(shè)計(jì):將電路圖轉(zhuǎn)化為物理掩模圖形。必須考慮器件匹配、寄生參數(shù)提取、天線效應(yīng)、閂鎖效應(yīng)以及設(shè)計(jì)規(guī)則檢查(DRC)和版圖與電路圖一致性檢查(LVS)。

- 系統(tǒng)級(jí)考量:在更大的系統(tǒng)背景下,MOSFET電路的性能需與電源管理、時(shí)鐘分布、信號(hào)完整性和熱管理協(xié)同優(yōu)化。

###

MOSFET電路知識(shí)是集成電路設(shè)計(jì)的通用語(yǔ)言和核心工具。從最基礎(chǔ)的開關(guān)行為到應(yīng)對(duì)最前沿的工藝挑戰(zhàn),深刻理解并嫻熟運(yùn)用MOSFET,是區(qū)分優(yōu)秀工程師與普通工程師的關(guān)鍵。隨著集成電路不斷向更高性能、更低功耗、更多功能集成邁進(jìn),MOSFET及其衍生技術(shù)仍將是推動(dòng)這場(chǎng)革命的永恒引擎。持續(xù)學(xué)習(xí)其深層次的物理機(jī)制和設(shè)計(jì)藝術(shù),是每一位IC設(shè)計(jì)者職業(yè)生涯中不可或缺的旅程。