隨著信息技術的飛速發展,數字集成電路在現代電子系統中扮演著核心角色。Verilog HDL作為一種硬件描述語言,已成為數字電路設計領域的重要工具,廣泛應用于從邏輯設計到系統集成的各個環節。本文將探討Verilog HDL的基本原理及其在數字集成電路設計中的實際應用。

一、Verilog HDL的基本原理

Verilog HDL(Hardware Description Language)誕生于1983年,由Gateway Design Automation公司開發,后來成為IEEE標準(IEEE 1364)。它是一種用于描述數字系統結構和行為的語言,支持不同抽象層次的設計,包括門級、寄存器傳輸級(RTL)和行為級。

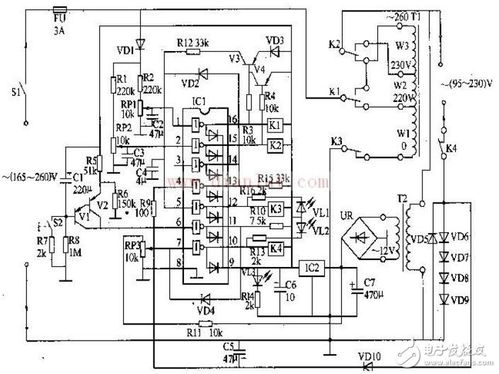

Verilog的核心思想是將硬件電路建模為并行執行的模塊。與軟件編程語言不同,Verilog代碼描述的是硬件的并發特性。基本組成元素包括模塊(module)、端口(port)、信號(wire/reg)和過程塊(always/initial)。模塊是Verilog設計的基本單元,通過端口與外部環境交互;信號代表硬件連接;過程塊則用于描述時序和組合邏輯。

二、數字集成電路設計流程

基于Verilog的數字集成電路設計通常遵循標準化流程:

- 設計規范:明確電路功能、性能和接口要求。

- 行為級描述:使用Verilog高級抽象描述系統功能。

- RTL級設計:將行為級代碼轉換為可綜合的寄存器傳輸級描述。

- 功能仿真:驗證設計邏輯的正確性。

- 邏輯綜合:將RTL代碼轉換為門級網表。

- 布局布線:將門級網表映射到物理芯片。

- 時序驗證:確保設計滿足時序要求。

- 芯片制造:生成最終的集成電路。

三、Verilog在集成電路設計中的應用

Verilog在現代集成電路設計中應用廣泛:

- 處理器設計:從簡單的微控制器到復雜的多核CPU,Verilog用于描述指令集架構、流水線和緩存系統。

- 通信芯片:網絡交換機、路由器和無線通信基帶處理器都依賴Verilog實現數字信號處理和數據包處理功能。

- 存儲控制器:DDR、Flash和SSD控制器使用Verilog實現復雜的數據調度和錯誤校正算法。

- 人工智能加速器:專用的AI芯片使用Verilog描述矩陣運算單元和神經網絡加速架構。

- 汽車電子:高級駕駛輔助系統(ADAS)中的傳感器融合和決策模塊都基于Verilog設計。

四、設計實例:簡單的ALU模塊

以下是一個基于Verilog的4位算術邏輯單元(ALU)的簡化示例:

module alu_4bit(

input [3:0] a, b,

input [1:0] op,

output reg [3:0] result,

output reg zero_flag

);

always @(*) begin

case(op)

2'b00: result = a + b; // 加法

2'b01: result = a - b; // 減法

2'b10: result = a & b; // 邏輯與

2'b11: result = a | b; // 邏輯或

default: result = 4'b0000;

endcase

zero_flag = (result == 4'b0000);

end

endmodule這個簡單的ALU模塊展示了Verilog如何清晰描述組合邏輯功能,包括算術運算、邏輯運算和狀態標志生成。

五、發展趨勢與挑戰

隨著工藝節點不斷縮小,Verilog設計面臨新的挑戰:

- 功耗優化:需要更精細的功耗建模和低功耗設計技術。

- 時序收斂:在深亞微米工藝下,時序收斂變得更加困難。

- 驗證復雜性:系統規模增大導致驗證工作量呈指數增長。

- 系統級集成:需要更高級別的抽象和系統級設計方法。

為應對這些挑戰,業界正在發展SystemVerilog、UVM驗證方法學和高層次綜合(HLS)等新技術。

Verilog HDL作為數字集成電路設計的基石,其重要性將持續增強。掌握Verilog不僅需要理解語言語法,更需要深入理解數字電路原理和系統設計思想。隨著人工智能、物聯網和5G等新興技術的發展,Verilog設計師將在推動技術進步中發揮關鍵作用。