專用集成電路(ASIC)的開發(fā)是一個(gè)復(fù)雜而系統(tǒng)的工程,涉及多個(gè)階段和跨學(xué)科協(xié)作。其開發(fā)過(guò)程通常包括需求分析、架構(gòu)設(shè)計(jì)、電路設(shè)計(jì)、驗(yàn)證、物理實(shí)現(xiàn)、制造和測(cè)試等環(huán)節(jié)。

在需求分析階段,開發(fā)團(tuán)隊(duì)需明確ASIC的功能、性能指標(biāo)、功耗要求及成本約束。這一階段通常與客戶或系統(tǒng)工程師密切合作,確保設(shè)計(jì)目標(biāo)與實(shí)際應(yīng)用場(chǎng)景匹配。

接下來(lái)是架構(gòu)設(shè)計(jì),工程師將功能需求轉(zhuǎn)化為高層次架構(gòu)方案,確定模塊劃分、數(shù)據(jù)流和控制邏輯。此階段可能使用硬件描述語(yǔ)言(如Verilog或VHDL)進(jìn)行行為級(jí)建模,并通過(guò)仿真驗(yàn)證架構(gòu)的可行性。

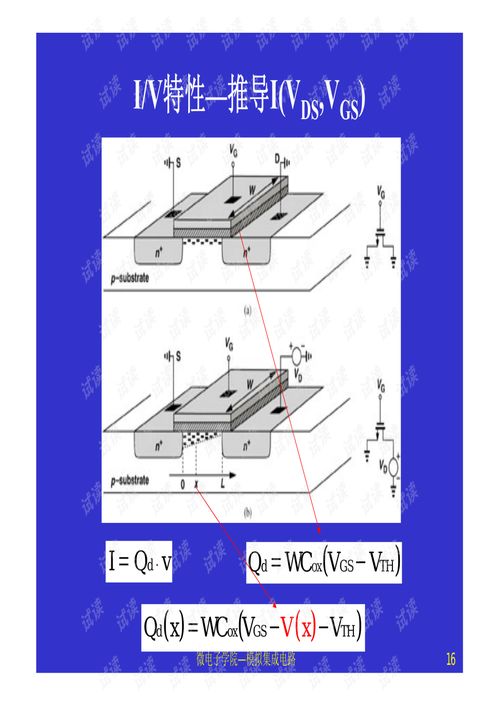

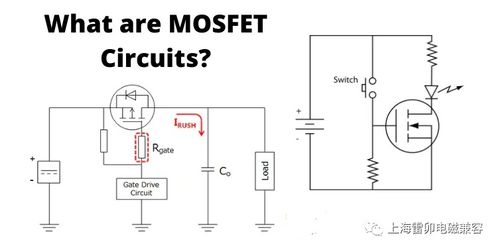

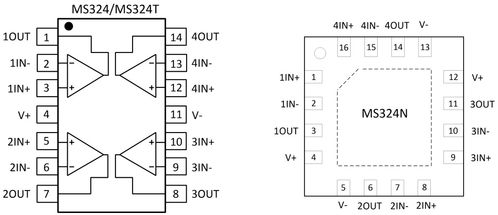

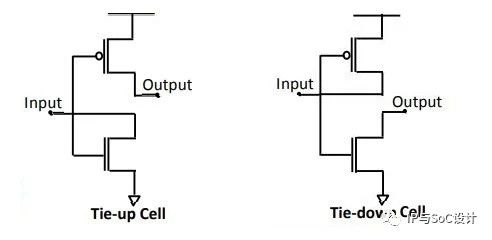

電路設(shè)計(jì)階段包括邏輯設(shè)計(jì)和物理設(shè)計(jì)。邏輯設(shè)計(jì)將架構(gòu)轉(zhuǎn)換為門級(jí)網(wǎng)表,利用綜合工具優(yōu)化時(shí)序和面積;物理設(shè)計(jì)則處理布局布線,確保信號(hào)完整性和功耗分布合理。此時(shí)需要充分考慮工藝庫(kù)的特性,如基于臺(tái)積電或三星的納米制程。

驗(yàn)證貫穿整個(gè)開發(fā)周期,包括功能驗(yàn)證、時(shí)序驗(yàn)證和形式驗(yàn)證。通過(guò)搭建測(cè)試平臺(tái)和回歸測(cè)試,確保設(shè)計(jì)在所有 corner case 下均能正常工作。現(xiàn)代ASIC設(shè)計(jì)常采用UVM等驗(yàn)證方法學(xué)以提高效率。

物理實(shí)現(xiàn)后,設(shè)計(jì)進(jìn)入制造階段,通過(guò)光刻、蝕刻等半導(dǎo)體工藝在晶圓上生成電路。隨后進(jìn)行封裝和測(cè)試,剔除缺陷芯片,并對(duì)成品進(jìn)行特性分析和可靠性評(píng)估。

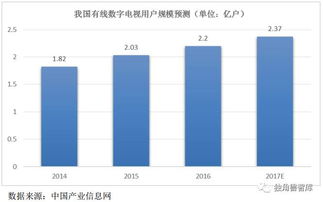

值得注意的是,隨著AI和物聯(lián)網(wǎng)的發(fā)展,ASIC設(shè)計(jì)日益傾向于異構(gòu)集成和低功耗優(yōu)化。例如,針對(duì)機(jī)器學(xué)習(xí)的加速器常采用定制化數(shù)據(jù)路徑,而邊緣計(jì)算芯片則強(qiáng)調(diào)能效比。

ASIC開發(fā)是資金密集、技術(shù)密集且周期漫長(zhǎng)的過(guò)程,需要設(shè)計(jì)團(tuán)隊(duì)具備深厚的半導(dǎo)體物理、電子工程和計(jì)算機(jī)科學(xué)知識(shí)。成功的ASIC不僅能提升系統(tǒng)性能,還能在特定領(lǐng)域形成技術(shù)壁壘,成為企業(yè)核心競(jìng)爭(zhēng)力的重要組成部分。